# **Space engineering**

## **Spacecraft discrete interfaces**

ECSS Secretariat ESA-ESTEC Requirements & Standards Division Noordwijk, The Netherlands

This Standard is one of the series of ECSS Standards intended to be applied together for the management, engineering and product assurance in space projects and applications. ECSS is a cooperative effort of the European Space Agency, national space agencies and European industry associations for the purpose of developing and maintaining common standards.

Requirements in this Standard are defined in terms of what shall be accomplished, rather than in terms of how to organize and perform the necessary work. This allows existing organizational structures and methods to be applied where they are effective, and for the structures and methods to evolve as necessary without rewriting the standards.

The formulation of this Standard takes into account the existing ISO 9000 family of documents.

This Standard has been prepared by the ECSS-E-50-14 Working Group, reviewed by the ECSS Executive Secretariat and approved by the ECSS Technical Authority.

#### Disclaimer

ECSS does not provide any warranty whatsoever, whether expressed, implied, or statutory, including, but not limited to, any warranty of merchantability or fitness for a particular purpose or any warranty that the contents of the item are error-free. In no respect shall ECSS incur any liability for any damages, including, but not limited to, direct, indirect, special, or consequential damages arising out of, resulting from, or in any way connected to the use of this standard, whether or not based upon warranty, contract, tort, or otherwise; whether or not injury was sustained by persons or property or otherwise; and whether or not loss was sustained from, or arose out of, the results of, the item, or any services that may be provided by ECSS.

Published by:ESA Requirements and Standards Division<br/>ESTEC, P.O. Box 299,<br/>2200 AG Noordwijk<br/>The NetherlandsCopyright:2007 © by the European Space Agency for the members of ECSS

## Change log

| ECSS-E-50-14A | 18 December 2007 | First issue |

|---------------|------------------|-------------|

|               |                  |             |

## Contents

| Chang   | ge log                                                           |    |

|---------|------------------------------------------------------------------|----|

| 1 Scop  | Je                                                               | 7  |

| 2 Norr  | native references                                                | 8  |

| 3 Tern  | ns, definitions and abbreviated terms                            | 9  |

| 3.1     | Terms from other standards                                       |    |

| 3.2     | Terms and definitions specific to the present standard           | 9  |

| 3.3     | Abbreviated terms                                                |    |

| 3.4     | Conventions                                                      |    |

| 4 Gen   | eral                                                             |    |

| 4.1     | Introduction                                                     |    |

| 4.2     | Architectural concepts                                           |    |

| 5 Anal  | logue signal interfaces                                          |    |

| 5.1     | Overview                                                         |    |

| 5.2     | Analogue signal monitor (ASM) interface                          |    |

| 5.3     | Temperature sensors monitor (TSM) interface                      |    |

| 6 Bi-le | vel discrete input interfaces                                    |    |

| 6.1     | Bi-level discrete monitor (BDM) interface                        |    |

| 6.2     | Bi-level switch monitor (BSM) interface                          |    |

| 7 Puls  | ed command interfaces                                            |    |

| 7.1     | High power command (HPC) interfaces                              |    |

| 7.2     | Low power command (LPC) interface                                |    |

| 8 Seria | al digital interfaces                                            |    |

| 8.1     | Foreword                                                         |    |

| 8.2     | General principles of serial digital interfaces                  |    |

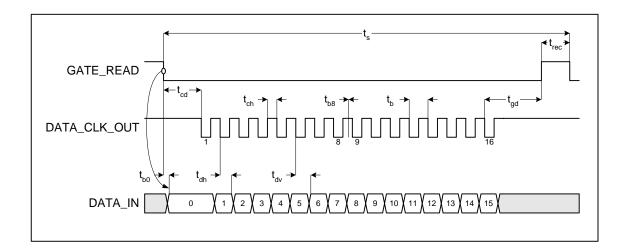

| 8.3     | 16-bit input serial digital (ISD) interface                      |    |

| 8.4     | 16-bit output serial digital (OSD) interface description         | 50 |

| 8.5     | 16-bit bi-directional serial digital (BSD) interface description |    |

| 8.6     | Serial digital interface electrical circuits description         | 55 |

| 8.7     | Balanced differential serial digital interface signals           | 55 |

| 8.8     | Serial digital interface circuit electrical characteristics      |    |

| Annex   | A Tailoring guidelines                                           |    |

| Empty   | y applicability matrix                                           | 61 |

## Figures

| Figure 1: Bit numbering convention                                                                                 |    |

|--------------------------------------------------------------------------------------------------------------------|----|

| Figure 2: Timing diagram conventions                                                                               |    |

| Figure 3: Signal timing and measurement references                                                                 |    |

| Figure 4: Architectural context of interfaces defined in this standard                                             | 14 |

| Figure 5: General scheme of redundant unit's cross-strapping                                                       |    |

| Figure 6: Example scheme for Single source – Dual receiver cross-strapping                                         |    |

| Figure 7: Example scheme for Dual source – Single receiver cross-strapping                                         |    |

| Figure 8: Cable capacitance definitions                                                                            | 19 |

| Figure 9: Analogue signal monitor (single ended source) interface arrangement                                      | 23 |

| Figure 10: Analogue signal monitor (differential source) interface arrangement                                     |    |

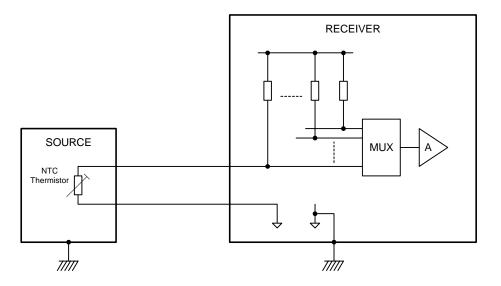

| Figure 11: TSM1 reference model                                                                                    |    |

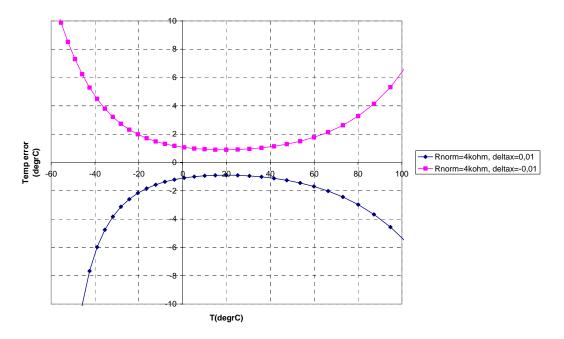

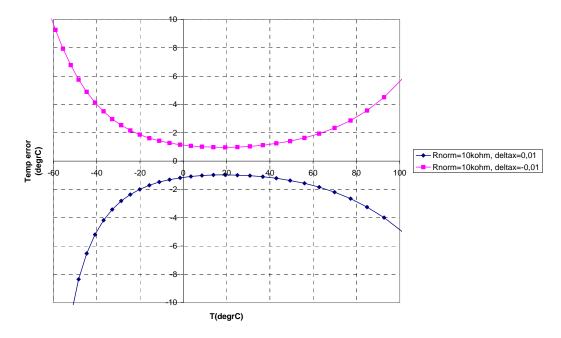

| Figure 12: Requirement for $\Delta R_{th}/R_{th}$ as a function of $R_{NORM}$ and $R_{th}$ . $\Delta x = \pm 0.01$ |    |

| Figure 13: TSM1 interface arrangement                                                                              |    |

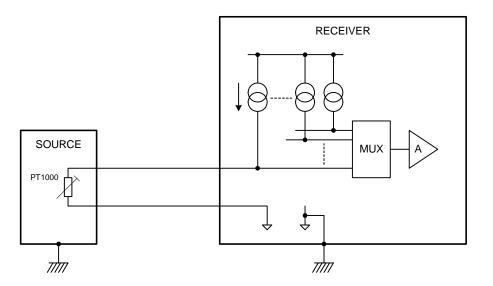

| Figure 14: TSM2 interface arrangement                                                                              |    |

| Figure 15: Example TSM1 and 4K3A354 thermistor                                                                     |    |

| Figure 16: Example TSM1 and YSI44907 thermistor                                                                    |    |

| Figure 17: Example TSM2 and PT1000 thermistor                                                                      |    |

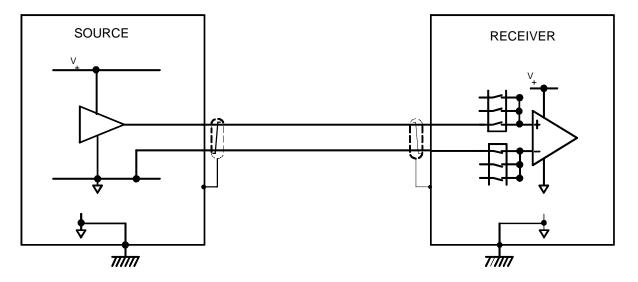

| Figure 18: BDM Interface configuration                                                                             |    |

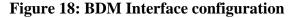

| Figure 19: Switch status circuit interface arrangement                                                             |    |

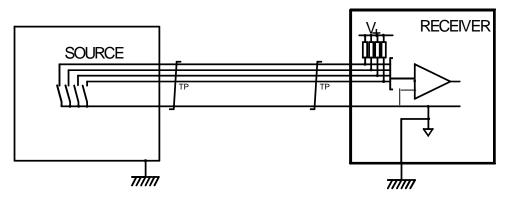

| Figure 20: HPC interface arrangement                                                                               |    |

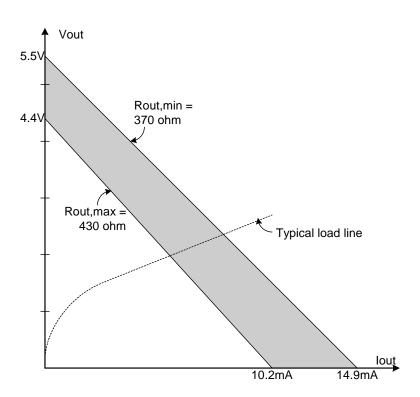

| Figure 21: LPC active signal output voltage vs. load current                                                       |    |

| Figure 22: LPC-P and LPC-S interface arrangement                                                                   |    |

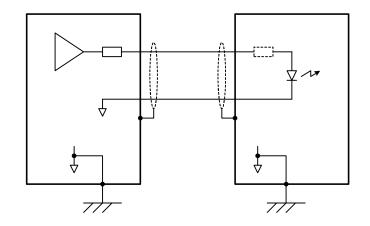

| Figure 23: 16-bit input serial digital (ISD) interface signal arrangement                                          |    |

| Figure 24: 16-bit input serial digital (ISD) interface                                                             |    |

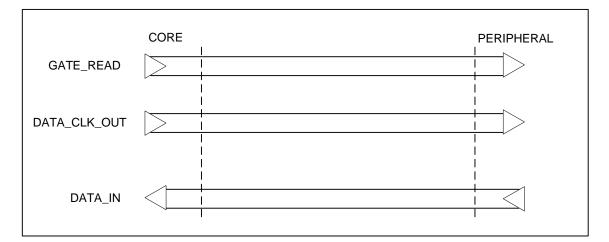

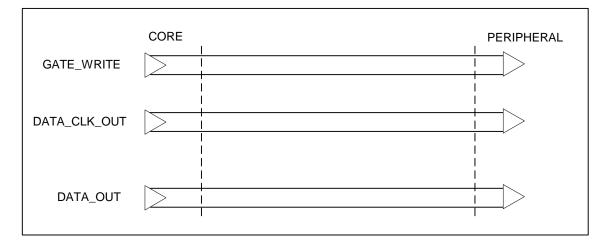

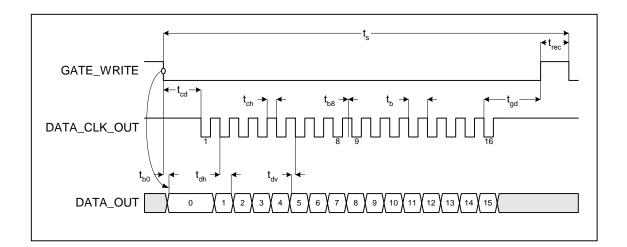

| Figure 25: 16-bit output serial digital (OSD) interface signal arrangement                                         | 51 |

| Figure 26: 16-bit output serial digital (OSD) interface                                                            | 51 |

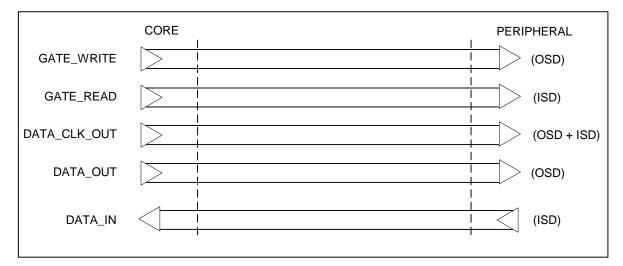

| Figure 27: 16-bit bi-directional serial digital interface signal arrangement                                       |    |

| Figure 28: Balanced differential circuits for serial digital interfaces                                            |    |

| Figure 29: Example of serial digital interface arrangement                                                         |    |

| Figure 30: Threshold levels for ECSS-E-50-14 differential circuits                                                 |    |

### Tables

| Table 1: Analogue signal monitor source circuit characteristics | 21 |

|-----------------------------------------------------------------|----|

| Table 2: Analogue signal receiver circuit characteristics       |    |

| Table 3: TSM1 source circuit characteristics                    |    |

| Table 4: TSM1 receiver circuit characteristics                  |    |

| Table 5: TSM2 source characteristics                            |    |

| Table 6: TSM2 receiver characteristics                          |    |

| Table 7: BDM source characteristics                             |    |

| Table 8: BDM receiver characteristics                           |    |

| Table 9: Switch source characteristics                          |    |

| Table 10: Switch receiver characteristics                       |    |

| Table 11: LV-HPC source characteristics                         |    |

| Table 12: LV-HPC receiver characteristics                       | 39 |

| Table 13: HV-HPC source characteristics                         | 39 |

| Table 14: HV-HPC receiver characteristics                       | 40 |

| Table 15: HC-HPC source characteristics                                |    |

|------------------------------------------------------------------------|----|

| Table 16: HC-HPC receiver characteristics                              | 41 |

| Table 17: LPC source characteristics                                   |    |

| Table 18: LPC receiver characteristics                                 |    |

| Table 19: 16-bit input serial digital (ISD) interface characteristics  |    |

| Table 20: t <sub>b</sub> values                                        | 50 |

| Table 21: 16-bit output serial digital (OSD) interface characteristics |    |

| Table 22: Serial digital interface electrical characteristics          |    |

|                                                                        |    |

## 1 Scope

This standard specifies a common set of spacecraft onboard electrical interfaces for sensor acquisition and actuator control. The interfaces specified in this standard are the traditional point-to-point interfaces that are commonly used on modern spacecraft.

The interfaces specified in this standard include analogue and discrete digital interfaces used for status measurement and control, as well as point-to-point serial digital interfaces used for digital data acquisition and commanding of devices.

This standard specifies:

- interface signal identification;

- interface signal waveforms;

- signal timing requirements;

- signal modulation;

- voltage levels;

- input and output impedance;

- overvoltage protection requirements;

- bit ordering in digital data words;

- cabling requirements where appropriate.

This standard does not cover:

- connector requirements;

- digital data word semantics;

- message or block formats and semantics.

Connector requirements are not covered because these are normally mission or project specific. The goal of this standard is to establish a single set of definitions for these interfaces and to promote generic implementations that can be re-used throughout different missions.

When referred, the present standard is applicable as a complement of the already existing interface standards ANSI/TIA/EIA-422B-1994 and ITU-T Recommendation V.11 (Previously "CCITT Recommendation") – (03/93).

Guidance for tailoring of the present standard can be found in Annex A.

## 2 Normative references

The following dated normative documents are called by the requirements of this ECSS Standard and therefore constitute requirements to it. Subsequent amendments to, or revisions of any of these publications do not apply.

NOTE However, parties to agreements based on this ECSS Standard are encouraged to investigate the possibility of applying the most recent editions of the normative documents indicated be-low.

ECSS-P-001B

#### ECSS - Glossary of terms

ANSI/TIA/EIA-422B-1994

ITU-T Recommendation V.11 (Previously "CCITT Recommendation") – (03/93) Electrical characteristics of balanced voltage digital interface circuits

Electrical characteristics for balanced double-current interchange circuits operating at data signalling rates up to 10 Mbit/s

## 3 Terms, definitions and abbreviated terms

### 3.1 Terms from other standards

For the purpose of this Standard, the terms and definitions from ECSS-P-001B apply.

### 3.2 Terms and definitions specific to the present standard

#### 3.2.1 circuit

conducting path which conveys a signal across the interface from the signal source to the signal destination

NOTE A circuit includes the cable conductor, any intervening connectors, and any circuit elements such as protection resistors and coupling capacitors, which make up the signal path.

#### 3.2.2 DHS data interchange bus

underlying communication medium which connects the DHS core elements

NOTE This can consist of more than one physical bus.

#### 3.2.3 DHS core element

component of a data handling system which has a direct connection to the DHS data interchange bus

EXAMPLE Bus controllers and remote terminals.

#### 3.2.4 DHS peripheral element

component of a data handling system which does not have a direct connection to the DHS data interchange bus

EXAMPLE Sensors and actuators.

#### 3.2.5 ground displacement voltage

voltage difference between source and receiver ground references

NOTE Users are encouraged to use this definition instead of 'common mode voltage' that is not correct when referring to the academic definition.

#### 3.2.6 accuracy

closeness of a measurement to the actual quantity being measured

NOTE For the purposes of this Standard it is expressed as percentage of the full measurement range or as an absolute value.

#### 3.2.7 time reference point

point at which a time interval starts or ends

NOTE It is the mid point between the nominal high and nominal low signal voltages.

## 3.3 Abbreviated terms

The following abbreviations are used within this document:

| Abbreviation | Meaning                         |

|--------------|---------------------------------|

| A/D          | analogue to digital             |

| ADC          | analogue digital converter      |

| ASM          | analogue signal monitor         |

| BDM          | bi-level discrete monitor       |

| BSD          | bi-directional serial digital   |

| BSM          | bi-level switch monitor         |

| СМ           | common mode                     |

| DHS          | data handling system            |

| HPC          | high power command              |

| НС-НРС       | high current high power command |

| HV-HPC       | high voltage high power command |

| ISD          | input serial digital            |

| LPC          | low power command               |

| LPC-P        | low power command, pulsed       |

| LPC-S        | low power command, static       |

| LSB          | least significant bit           |

| LV-HPC       | low voltage high power command  |

| MSB          | most significant bit            |

| OBDH         | on-board data handling          |

| OSD          | output serial digital           |

| TSM          | temperature sensors monitor     |

### 3.4 Conventions

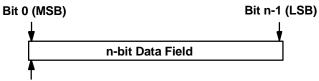

#### 3.4.1 Bit numbering convention

The most significant bit of an n-bit field is:

- numbered bit 0 (zero),

- the first bit transmitted, and

• the leftmost bit on a format diagram.

- The least significant bit of an n-bit field is:

- numbered bit n-1,

- the last bit transmitted, and

- the rightmost bit on a format diagram.

This convention is illustrated in Figure 1.

First Bit Transmitted

**Figure 1: Bit numbering convention**

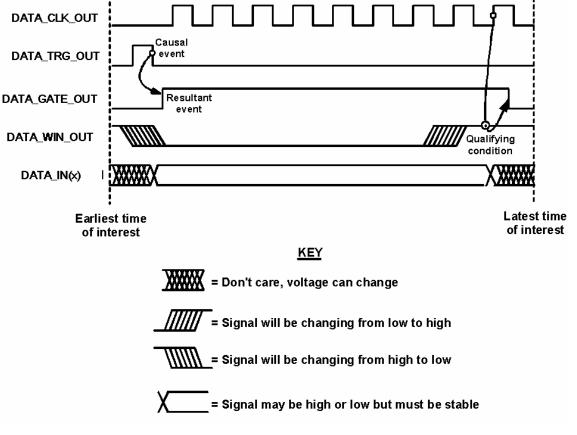

#### 3.4.2 Timing diagram conventions

Timing diagrams are always drawn with the earliest time on the left and time advancing to the right.

Where an event, such as a transition, in one signal causes an event in another, the two events are linked by an arrow with the tail of the arrow on the causal event and the head of the arrow on the resultant event.

Where an event in one signal is the result of an event in another signal and a qualifying condition in one or more other signals, the connecting arrow is associated with the governing condition using a bull's eye.

These conventions, together with other timing diagram symbols, are shown in Figure 2.

Figure 2: Timing diagram conventions

#### 3.4.3 Signal and signal event naming convention

Signals are named in a manner which indicates the function of that signal. For example, a clock used for data bit sampling can be called DATA\_CLK.

Control signal naming is meaningful with the function of the signal, its direction, and its assertion levels all indicated. The direction is indicated with respect to the DHS core element so that an OUT signal is an output, i.e. driven from the core element. An IN signal is an input to the core element. For example, a signal carrying data out of the core element is named DATA\_OUT.

Control signal assertion or validity levels are indicated within brackets. For example, a gate output signal which is asserted when low is named GATE\_OUT(L). Similarly, an input signal which indicates that a device is ready when it is high is named READY\_IN(H).

Signal events such as transitions and pulses are also named symbolically using " $_{UP}$ " and " $_{DOWN}$ " indication. For example, START $_{UP}$  indicates a rising edge event on the start signal, and STOP $_{DOWN}$  indicates a falling edge on the stop signal. RUN $_{UPDOWN}$  indicates a positive going pulse on the run signal, while HALT $_{DOWNUP}$  indicates a negative going pulse on the halt signal.

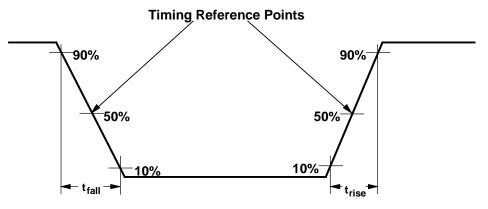

#### 3.4.4 Signal timing and measurement references

Signal rise and fall times, which are shown in Figure 3, are measured between 10% and 90% of the difference between the nominal low and nominal high signal voltages, as it can be seen in the mentioned figure.

**Figure 3: Signal timing and measurement references**

## 4 General

## 4.1 Introduction

This standard defines electrical interfaces for use onboard spacecraft to connect simple devices such as sensors and actuators to the data handling system. The interfaces defined are:

- analogue signal interfaces (clause 5)

- o analogue signal monitor

- temperature sensor monitor

- bi-level discrete input interfaces (clause 6)

- o bi-level discrete monitor

- bi-level switch status monitor

- command interfaces (clause 7)

- high power pulse command

- low power command

- serial digital interfaces (clause 8).

Each interface is defined in terms of the electrical and timing characteristics of the signals comprising that interface. Connectors for the interfaces are not defined because these are often highly project dependent. Cabling characteristics are defined where appropriate.

For the serial digital interfaces, the data content of the digital words is not defined since this is the subject of higher level protocol standards beyond the scope of this Standard.

Unless otherwise stated, specified performances are applicable when both source and receiver are powered.

## 4.2 Architectural concepts

#### 4.2.1 Overview

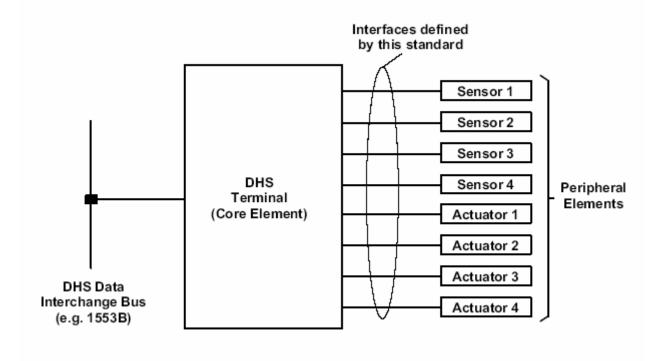

The interfaces specified in this Standard are intended to connect DHS core elements to DHS peripheral elements as shown in Figure 4. However, there are no technical reasons to prevent these interfaces being used between core elements where it is appropriate to do so, and this Standard does not preclude such a configuration.

A peripheral element can have more than one user interface and also user interfaces of different types, depending on its function and design. For example, some sensors can set threshold levels or sensitivities by means of data written to them. In this case that sensor can use an output serial digital interface to write the data in addition to an input serial digital interface to read the sensor value. Alternatively, some devices are signalled to indicate that they are commanded to acquire a data sample. In that case they can use a serial digital interface together with a pulse interface.

#### Figure 4: Architectural context of interfaces defined in this standard

#### 4.2.2 General failure tolerance

#### 4.2.2.1 Input interfaces

Among other failure cases, receivers shall:

- a. Not be stressed and not show degraded performance when input is open circuit except on the input I/F that is open circuit.

- b. Not be stressed and not show degraded performance when input is short circuit to ground except on the input I/F that is short circuit.

- NOTE No specific performance requirements are imposed while in this status.

#### 4.2.2.2 Output interfaces

Among other failure cases, transmitters shall:

- a. Not be stressed and not show degraded performance when output is open circuit except on the output I/F that is open circuit.

- b. Not be stressed when output is short circuit to ground.

- NOTE No specific performances requirement is imposed while in this status.

#### 4.2.3 Interface control during power cycling

#### 4.2.3.1 Input interfaces

- a. Input interfaces shall not be damaged or harmed during power cycling conditions taking the transmitting side state into account in any normal state or applicable failure condition.

- b. Receivers shall not deliver power to the other circuits or be stressed when the unit is OFF while connected to an active driver.

NOTE No specific performance requirements are imposed while in this status.

#### 4.2.3.2 Output interfaces

- a. Output interfaces shall not be damaged or harmed during power cycling conditions when the receiving side state is in any normal state or specified failure condition.

- NOTE No specific performance requirements are imposed while in this status.

- b. For pulse commands it shall be ensured that spurious commands are not emitted during power cycling that exceed activation limits for the receivers.

- NOTE 1 For pulse commands, see Clause 7.

- NOTE 2 This requirement does not specify the prevention of spurious pulses, but ensures either that:

- spurious pulses are below the threshold for the receiver, or

- the spurious pulse duration is short enough to not drive the load into activation (for example a relay coil or opto-coupler diode).

#### 4.2.4 Cross-strapping

#### 4.2.4.1 General

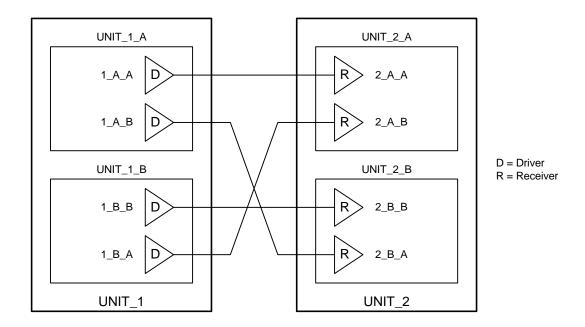

- a. For 2 units (UNIT\_1 & UNIT\_2), that can be used in redundancy, the cross-strapping of drivers and receivers shall be as specified in Figure 5, and meet the following conditions:

- 1. The UNIT\_2\_A I/F is capable to receive:

- A signal from the UNIT\_1\_A I/F through a dedicated link

- A signal from the UNIT\_1\_B I/F through a dedicated link

- 2. The UNIT\_2\_B I/F shall is capable to receive:

- A signal from the UNIT 1 A I/F through a dedicated link

- A signal from the UNIT 1 B I/F through a dedicated link

- 3. The UNIT 1 A I/F is capable to deliver:

- A signal to the UNIT 2 A I/F through a dedicated link

- A signal to the UNIT 2 B I/F through a dedicated link

- 4. The UNIT\_1\_B I/F is capable to deliver:

- A signal to the UNIT\_2\_A I/F through a dedicated link.

- A signal to the UNIT\_2\_B I/F through a dedicated link.

- b. To achieve full cross-strapping benefits, in terms of reliability, any potential common failure of UNIT\_1\_A and UNIT\_1\_B drivers and UNIT\_2\_A and UNIT\_2\_B receivers shall be avoided.

#### Figure 5: General scheme of redundant unit's cross-strapping

#### 4.2.4.2 Immunity at UNIT\_2 level

- a. Under the condition (Receiver = ON linked to Transmitter = OFF of UNIT\_1), in the configuration where UNIT\_1 driver is OFF and UNIT\_2 receiver is ON, the information received by this receiver shall not disturb the valid information received by the other receiver (linked to a Transmitter ON).

- NOTE In this configuration the electrical status at receiver output is stable (due to hysteresis) but possibly unknown (logical "1" or "0").

- b. It should be ensured that any input signal is in a known (inactive) stable state when driver is OFF.

- c. If b. above is not met, a validation / inhibition stage at the receiver output of UNIT\_2 should be implemented.

- NOTE For example, the validation of the path can be made by a dedicated direct command arriving from UNIT\_1, which inhibits the UNIT\_2 receiver output unused (if such a configuration has been thoroughly designed with respect to failure cases).

#### 4.2.4.3 Protections at UNIT\_1 driver level

Under the condition (Transmitter = OFF linked to Receiver = ON of UNIT\_2), whether powered or not, UNIT\_1 drivers shall withstand any receiver characteristics as described in Clauses 5 to 8.

#### 4.2.4.4 Protections at UNIT\_2 receiver level

Under the condition (Receiver = OFF linked to Transmitter = ON of UNIT\_1), whether powered or not, UNIT\_2 receivers shall withstand any driver characteristics as described in Clauses 5 to 8.

#### 4.2.5 Harness cross-strapping

#### 4.2.5.1 Overview

Harness cross-strapping is applied when heritage units, without classical cross-strapping interfaces, are used, in the case that a single redundant unit is interfaced to both a nominal and redundant system. If the spacecraft is severely mass-limited, harness cross-strapping can be used instead.

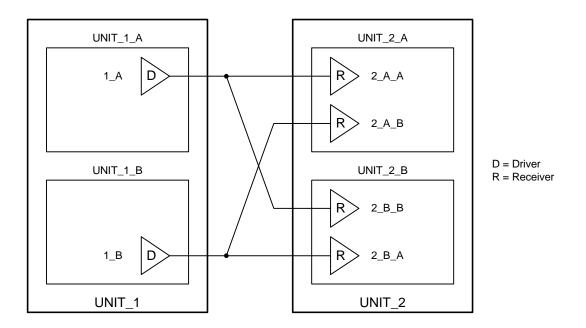

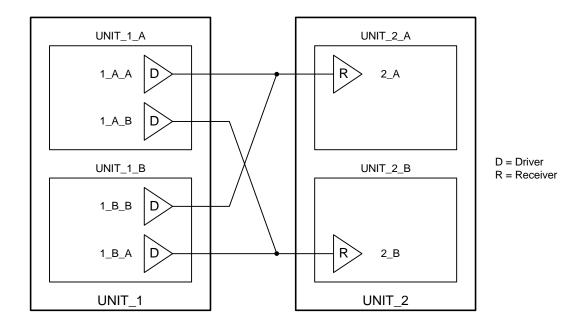

Harness cross-strapping can be used in two configurations:

- Single source Dual receiver configuration, as shown in Figure 6.

- Dual source Single receiver configuration, as shown in Figure 7.

The Single source – Dual receiver configuration is typically applied for BSM interfaces as described in subclause 6.2.

The Dual source – Single Receiver configuration is typically applied for HPC interfaces as described in subclause 7.1.

Note that this harness cross-strapping can be performed by galvanic connections in harness, as indicated in Figure 6 and Figure 7. However, the equivalent configuration applies in case the physical inter-connection is performed either within the source or within the receiver unit. The general rules and protections as mentioned in this subclause apply then also for those cases.

Possible problems that can be introduced by harness cross-strapping include failure propagation, loading and leakage injection of the active I/F by the redundant, inactive circuit such that the active circuit does not meet its performance requirements, incompatibility of protection circuitry of a given circuit with either the Receiver I/F circuit or the Driver (see Figure 7) I/F circuit. Note that in general it is important to consider loading by the redundant, inactive circuit also when powered off, even if the inactive circuit is normally powered (hot redundancy).

**Figure 6: Example scheme for Single source – Dual receiver cross-strapping**

#### Figure 7: Example scheme for Dual source – Single receiver cross-strapping

#### 4.2.5.2 Provisions

- a. If harness cross-strapping is used, there shall be no mechanism whereby the failure of either the receiver or unit interface can propagate to the I/F of another, unrelated unit.

- NOTE This requirement refers to a common mode failure where a failure of one interface then propagates inside the receiver thereby affecting units unrelated to the original failure.

- b. If harness cross-strapping is used, the calculation of the overall system reliability shall include the potential degradation or damage of the I/F of a redundant unit due to the failure of other interface.

- NOTE This requirement refers to the failure on a nominal unit causing the inoperability of the cross-strap. This means that there is a reduction in the possible reliability of the cross-strap.

- c. If harness cross-strapping is used, the capability shall be provided to shut down the inoperable unit regardless of the failure mode

- NOTE This implies that the power can be removed from the unit by independent means such as disabling the power interface at the power distribution unit (e.g. with the means described in subclause 4.2.4.2)

- d. Under the condition (Transmitter = OFF linked to Receiver = ON of UNIT\_2), whether powered or not, UNIT\_1 drivers shall withstand any receiver characteristics as described in Clauses 5 to 8.

- e. Under the condition (Receiver = OFF linked to Transmitter = ON of UNIT\_1), whether powered or not, UNIT\_2 receivers shall withstand any driver characteristics as described in Clauses 5 to 8.

#### 4.2.6 Cable capacitance

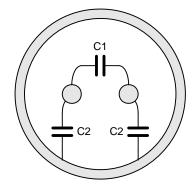

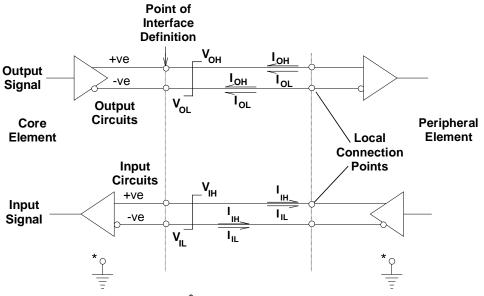

It is important that the DHS interfaces consider the capacitive loading by the harness. Figure 8 defines the capacitances involved for a twisted shielded pair cable.

#### Figure 8: Cable capacitance definitions

Effective capacitances can then be calculated according to:

- Core to core capacitance  $C_{CC} = C1 + \frac{C2}{2}$

- Core to shield capacitance  $C_{CS} = C2 + \frac{C1 \cdot C2}{C1 + C2}$

- Core to core capacitance with shield connected to one core  $C_{CT} = C1 + C2$

Note that the latter case applies typically when either the source or the receiver is single ended, which implies that both the shield and one of the core wires are grounded.

## 5 Analogue signal interfaces

### 5.1 Overview

The analogue signal interfaces are used for direct connection to a device which produces a continuous variable analogue voltage to indicate the value of the parameter being measured.

Usually, the analogue voltage produced by the sensor or a peripheral element is converted into a digital value within the core element to which it is connected. This Standard specifies the electrical characteristics of the analogue signal interfaces.

Two types of analogue interfaces are specified:

- Analogue signal monitor interface, ASM (see 5.2)

- Temperature sensors monitor interface, TSM (see 5.3)

## 5.2 Analogue signal monitor (ASM) interface

#### 5.2.1 General

#### 5.2.1.1 Overview

The analogue signal monitor interface is based on differential receiver circuit where both the high and low analogue signal lines are floating with respect to the receiver signal ground; the source interface can be either single ended or differential.

The analogue voltage provided is sampled intermittently by the core element. The precise frequency and the duration of the sampling interval depend on the A/D conversion service being used. However, the input impedance and capacitance exhibited by an analogue signal interface can differ when the input signal is actually being sampled compared with when it is not. As a consequence, different input impedance and capacitance requirements are provided for the different configurations.

In addition, the impedance seen when the receiver element is powered off is specified.

#### 5.2.1.2 Basic application scenario

The interface specified in this subclause is defined on the basis of a typical analogue signal monitoring application scenario, i.e.

- differential voltage range: 0 to 5 V or optionally 0 to 5,12 V;

- signal bandwidth:  $\leq 1$  Hz;

- NOTE This means that accuracy requirements are specified here assuming only slowly changing (quasi-static) signals. That does not prohibit, for instance, rapid transitions in signals, but accuracy is unspecified during such events.

- ground displacement voltage: ≤ ±1 V in the frequency range 0 to 1 kHz, falling at 20 dB per decade up to 1 MHz;

- conversion resolution: 12 bits<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup> Even if the overall channel accuracy requirement in 5.2.1.4 can be met also with an 8 bit ADC, it is important to note that in this case the ADC quantization error contributes  $\pm 0.2\%$  to the overall channel accuracy, thus normally a good practice is to use a 12 bit ADC.

NOTE The specified 12 bits resolution is not incompatible with use of ADC having 14 or even 16 bits resolution. In that case, LSB are "not significant".

#### 5.2.1.3 Applications other than the basic scenario

- a. If the actual scenario differs from the one defined in 5.2.1.2 (e.g. the specific application uses higher conversion accuracy or has different operational conditions, e.g. higher displacement), the interface shall not be directly used.

- NOTE In particular, ground displacement heavily affects the achievable conversion accuracy. Different scenario or specified performances can, for instance, ask for source impedance balancing.

- b. The modified interface shall be supported by an analysis of the overall system, including both interface source and receiver as well as interconnecting wiring.

#### 5.2.1.4 Acquisition of the analogue channels by the core element

The errors introduced by the DHS receiver analogue acquisition chain, including temperature, ground displacement voltage rejection, A/D conversion inaccuracy, herein specified source impedance and cable capacitance, supply voltage variations, lifetime and radiation effects shall be less than 1 % of the full scale.

#### 5.2.2 Analogue signal monitor interface

#### 5.2.2.1 Source circuit

The source circuit shall meet the characteristics specified in Table 1.

| Reference   | Characteristic                                                            | Value                                                                                                                                  |

|-------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 5.2.2.1 a   | Circuit type                                                              | Single ended or differential                                                                                                           |

| 5.2.2.1 b   | Transfer                                                                  | DC coupled                                                                                                                             |

| 5.2.2.1 c   | Zero reference                                                            | Signal ground – in case of differential source (ref Figure 10), the return signal's potential shall be equal to unit's chassis ground. |

| 5.2.2.1 d.1 | – Nominal output voltage range, V <sub>out</sub>                          | 0 V to +5 V <sup>a</sup>                                                                                                               |

| 5.2.2.1 d.2 |                                                                           | 0 V to +5,12 V                                                                                                                         |

| 5.2.2.1 e   | Output impedance, Z <sub>out</sub>                                        | $\leq 5 \ k\Omega$                                                                                                                     |

| 5.2.2.1 f   | Fault voltage tolerance, $V_{sft}$                                        | $\begin{array}{ccc} -17,5 \ V & to & +17,5 \ V & with & an \\ overvoltage & source & impedance \\ > 1,0 \ k\Omega \end{array}$         |

| 5.2.2.1 g   | Fault voltage emission, V <sub>sfe</sub>                                  | -16,5 V to +16,5 V                                                                                                                     |

|             | fter, the range $0 V - 5 V$ is the pread and A/D conversion is necessary. | eferred one. 5,12 V can be used if                                                                                                     |

#### Table 1: Analogue signal monitor source circuit characteristics

#### 5.2.2.2 Receiver circuit

The receiver circuit shall meet the characteristics specified in Table 2.

| Reference   | Characteristic                                                  | Value                                                            |

|-------------|-----------------------------------------------------------------|------------------------------------------------------------------|

| 5.2.2.2 a   | Circuit type                                                    | Differential                                                     |

| 5.2.2.2 b   | Transfer                                                        | DC coupled                                                       |

| 5.2.2.2 c.1 |                                                                 | differential: 0 V to +5 V                                        |

| 5.2.2.2 c.2 | - Nominal input voltage range, V <sub>in</sub>                  | differential: 0 V to +5,12 V                                     |

| 5.2.2.2 d   | Ground displacement voltage, $V_{GD}$                           | -1 V to 1 V up to 1 kHz rolling-off at 20 dB/decade up to 1 MHz  |

| 5.2.2.2 e   | Differential input impedance (sampling), Z <sub>is</sub>        | $\geq 1 M\Omega$                                                 |

| 5.2.2.2 f   | Differential input impedance (not sampling), Z <sub>ins</sub>   | $\geq 10 \text{ M}\Omega$                                        |

| 5.2.2.2 g   | Differential input impedance (powered off), $Z_{\rm ioff}$      | $\geq 10 \text{ k}\Omega$                                        |

| 5.2.2.2 h   | Differential input capacitance (sampling), C <sub>is</sub>      | ≤ 1,5 μF                                                         |

| 5.2.2.2 i   | Differential input capacitance (not sampling), $C_{ins}$        | ≤ 1,5 μF                                                         |

| 5.2.2.2 ј   | Differential input capacitance (powered off), C <sub>ioff</sub> | ≤ 1,5 μF                                                         |

| 5.2.2.2 k   | Fault voltage emission, V <sub>rfe</sub>                        | -16,5 V to +16,5 V with a series impedance $\geq$ 1,0 k $\Omega$ |

| 5.2.2.21    | Fault voltage tolerance, V <sub>rft</sub>                       | -17,5V to +17,5 V                                                |

#### Table 2: Analogue signal receiver circuit characteristics

NOTE It is important to note that, in practical terms, cross-strapping in harness as defined in subclause 4.2.5 unless the  $Z_{ioff}$  is on the order of the M $\Omega$  is prevented by subclause 5.2.2.2 g.

#### 5.2.2.3 Harness

#### 5.2.2.3.1 Wire type

- a. The wire type should be twisted shielded lines.

- b. If above is not met, n-tuples shall be used.

- c. The shield shall be connected to the structure ground both on source and receiver sides.

#### 5.2.2.3.2 Core to shield capacitance

The capacitance  $C_{CT}$  shall be less than 2 nF.

#### 5.2.2.4 Interface arrangement

The electrical interface arrangement is depicted in Figure 9 and Figure 10, which show specific implementation to be taken as examples, but other implementations compliant to requirements are not excluded.

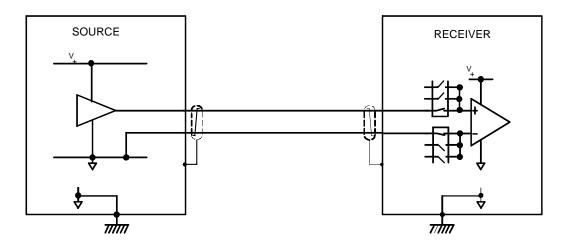

Figure 9: Analogue signal monitor (single ended source) interface arrangement

Figure 10: Analogue signal monitor (differential source) interface arrangement

### 5.3 Temperature sensors monitor (TSM) interface

#### 5.3.1 Overview

Temperature monitor channels are resistance measurement channels used for resistive temperature sensor acquisition.

The word "thermistor" is derived from the description "thermally sensitive resistor". Thermistors are further classified as "Positive Temperature Coefficient" devices (PTC devices) or "Negative Temperature Coefficient" devices (NTC devices):

- PTC devices are devices whose resistance increases as their temperature increases.

- NTC devices are devices whose resistance decreases as their temperature increases.

Two types of temperature monitor channels are addressed herein, referring to the two main classes of transducers available on the market:

- TSM1: Wide range resistance acquisition, suitable for NTC thermistors (negative temperature characteristic).

- TSM2: Limited range resistance acquisition, suitable for platinum (PT) type.

The conditioning configuration to be used depends on the transducer used. Both TSM1 and TSM2 interfaces are specified in terms of resistance measurement accuracy.

NOTE TSM1 can be used for platinum type sensors (PT), but that generally shows worse accuracy than a well adapted TSM2. Also, TSM2 can be used for NTC type of sensor, but the temperature range is then restricted.

Examples of corresponding measurement error in terms of temperature are given in subclause 5.3.5.5.

#### 5.3.2 TSM acquisition layout

- a. The thermistors shall be powered by the receiver, and

- b. The resulting voltage shall be utilised to feed a dedicated analogue channel.

- NOTE The objective of these requirements is that the receiver is able to directly interface with a passive thermistor:

#### 5.3.3 TSM acquisition resolution

At least 12-bit resolution shall be used.

NOTE Even if the overall channel accuracy requirement can be met also with an 8-bit ADC, it is important to note that in this case the ADC quantization error alone contributes  $\pm 0,2\%$  to the overall channel accuracy.

#### 5.3.4 TSM wire configuration

Dedicated input and return line from the current source to each thermistor channel shall be provided.

#### 5.3.5 TSM electrical characteristics

#### 5.3.5.1 TSM1

#### 5.3.5.1.1 Overview

The TSM1 interface has the following features:

- The measurable resistance range is specified from 0 to  $\infty \Omega$ .

- The interface is normalized with a parameter  $R_{NORM}$  ( $\Omega$ ), selectable within a specific range, where  $R_{NORM}$  is the resistance of the thermistor at a specified temperature point, where the highest temperature measurement accuracy is needed (the centre of the measurement range).

NOTE R<sub>NORM</sub> is selected per group of channels as a function of the sensor type and the temperature range of interest.

- The specified accuracy is expressed as a maximum error  $\pm \Delta x$ .

- The specified accuracy in terms of resistance is obtained from a formula including  $R_{NORM}$  and  $\Delta x$ .

- The resistance accuracy is specified at the DHS unit terminals, i.e. excluding any error contribution from the thermistor or harness.

#### 5.3.5.1.2 TSM1 error model

The maximum error in  $R_{th}$ ,  $\Delta R_{th}$ , shall be calculated as follows:

$$\Delta R_{th} = \frac{(R_{th} + R_{NORM})^2}{R_{NORM} - \Delta x \cdot (R_{th} + R_{NORM})} \cdot \Delta x, \qquad \text{if } R_{NORM} > \Delta x \cdot (R_{th} + R_{NORM}),$$

$$\Delta R_{th} = \infty \qquad \text{otherwise}$$

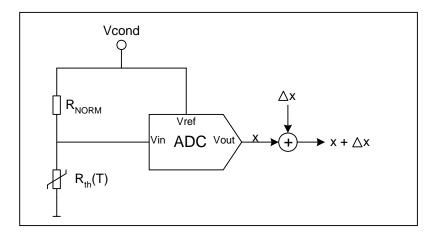

NOTE This calculation is based on the model of the TSM1 interface shown in Figure 11.  $R_{th}(T)$  symbolizes the resistance of the thermistor as a function of temperature T. The output from the ADC, x, has the range 0 to 1. The formula to express x as a function of  $R_{th}(T)$  is then:

$$x = \frac{V_{in}}{V_{ref}} = \frac{R_{ih}(T)}{R_{ih}(T) + R_{NORM}}$$

Figure 12 shows how the relative error in  $R_{th}$ ,  $\Delta R_{th}/R_{th}$ , varies with  $R_{th}$  with examples of  $R_{NORM}$  and  $\Delta x$ .

Examples have been evaluated for some specific thermistor types in subclause 5.3.5.5, showing the error in terms of temperature

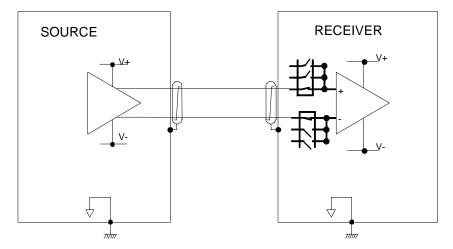

Figure 11: TSM1 reference model

Figure 12: Requirement for  $\Delta R_{th}/R_{th}$  as a function of  $R_{NORM}$  and  $R_{th}$ .  $\Delta x = \pm 0.01$ .

**5.3.5.1.3** TSM1 source electrical characteristics The characteristics in Table 3 shall be provided.

| Reference   | Characteristic                     | Value                                                                      |

|-------------|------------------------------------|----------------------------------------------------------------------------|

| 5.3.5.1.3 a | Circuit type                       | Floating Resistive sensor                                                  |

| 5.3.5.1.3 b | Transfer                           | DC coupled                                                                 |

| 5.3.5.1.3 c | Resistance range, R <sub>s</sub>   | $0 \text{ to } \infty \Omega$                                              |

| 5.3.5.1.3 d | Fault voltage tolerance, $V_{sft}$ | -17,5 V to +17,5 V with an overvoltage source impedance $\geq 1 \ k\Omega$ |

Table 3: TSM1 source circuit characteristics

**5.3.5.1.4** TSM1 receiver electrical characteristics The characteristics in Table 4 shall be provided.

| Reference   | Characteristic                                       | Value                                                                   |

|-------------|------------------------------------------------------|-------------------------------------------------------------------------|

| 5.3.5.1.4 a | Circuit type                                         | Single ended receiver with multiplexed inputs                           |

| 5.3.5.1.4 b | Transfer                                             | DC coupled                                                              |

| 5.3.5.1.4 c | Sensor injected power, Pi                            | $\leq 1 \text{ mW}$                                                     |

| 5.3.5.1.4 d | Measurement error, $\Delta x$                        | < ±0,01                                                                 |

| 5.3.5.1.4 e | Parameterized resistance range,<br>R <sub>NORM</sub> | 1 k $\Omega$ , to 10 k $\Omega$ , to be specified per group of channels |

| 5.3.5.1.4 f | Fault voltage emission, V <sub>rfe</sub>             | -16,5 V to +16,5 V with a source impedance of $\geq 1k\Omega$           |

| 5.3.5.1.4 g | Fault resistance tolerance, R <sub>rft</sub>         | Short circuit to ground                                                 |

#### Table 4: TSM1 receiver circuit characteristics

| NOTE | The low resistance range of $R_{NORM}$ is suitable for TSM receiver systems using power switched thermistor conditioning, where low impedance is of special interest to achieve fast settling. |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | The high resistance range of $R_{NORM}$ is more suitable for TSM receiver systems using continuous thermistor conditioning, where low power is crucial, but fast settling is of less concern   |

#### 5.3.5.1.5 Harness

- a. The wiring type shall be twisted n–tuple.

- b. The capacitance  $C_{CC}$  measured between the two core wires shall be less than or equal to 1 nF.

#### **5.3.5.1.6** Interface arrangement

The electrical I/F arrangement is specified in Figure 13.

- NOTE 1 Circuitry and resistors are indicative only; other implementations meeting the above requirements are not excluded.

- NOTE 2 In practical implementations a resistance to ground in the receiver is often used.

#### Figure 13: TSM1 interface arrangement

#### 5.3.5.2 TSM2

#### 5.3.5.2.1 Overview

The TSM2 interface has the following features:

- The measurable resistance range is specified from 0  $\Omega$  to up to R<sub>MAX</sub>.

- NOTE  $R_{MAX}$  can be seen as the maximum resistance of the thermistor in the temperature range of interest.

- R<sub>MAX</sub> can be chosen as characteristic of a group of channels within a specific range.

- The specified accuracy is expressed as a maximum error  $\pm \Delta x$ .

- The specified accuracy in terms of resistance is expressed as  $\Delta x \cdot R_{MAX}$ .

- The resistance accuracy is specified at the DHS unit terminals, i.e. excluding any error contribution from the thermistor or harness.

#### 5.3.5.2.2 TSM2 error model

The maximum error in  $R_{th}$ ,  $\Delta R_{th}$ , expressed as a function of  $\Delta x$ , shall be:

$\Delta R_{th} = R_{MAX} \cdot \Delta x$

5.3.5.2.3 TSM2 source electrical characteristics

The source shall meet the characteristics specified in Table 5.

| Table 5: TSM2 source characteristic |

|-------------------------------------|

|-------------------------------------|

| Reference   | Characteristic                            | Value                                                                                                                                                                                                          |

|-------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.3.5.2.3 a | Circuit type                              | Floating Resistive sensor                                                                                                                                                                                      |

| 5.3.5.2.3 b | Transfer                                  | DC coupled                                                                                                                                                                                                     |

| 5.3.5.2.3 c | Resistance range, R <sub>s</sub>          | $\begin{array}{l} 0 \ \Omega \ \text{to} \ R_{MAX} \\ R_s \ \text{is selected per group of channels as} \\ a \ \text{function of the sensor type and the} \\ \text{temperature range of interest} \end{array}$ |

| 5.3.5.2.3 d | Fault voltage tolerance, V <sub>sft</sub> | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                          |

#### 5.3.5.2.4 TSM2 receiver electrical characteristics

The receiver shall meet the characteristics specified in Table 6.

| Reference   | Characteristic                                      | Value                                                               |

|-------------|-----------------------------------------------------|---------------------------------------------------------------------|

| 5.3.5.2.4 a | Circuit type                                        | Single ended receiver with multiplexed inputs                       |

| 5.3.5.2.4 b | Transfer                                            | DC coupled                                                          |

| 5.3.5.2.4 c | Sensor injected power, P <sub>i</sub>               | $\leq 1 \text{ mW}$                                                 |

| 5.3.5.2.4 d | Measurement error, $\Delta x$                       | <±0,01                                                              |

| 5.3.5.2.4 e | Parameterized resistance range,<br>R <sub>MAX</sub> | $1 k\Omega$ to $5 k\Omega$ , to be specified per group of channels  |

| 5.3.5.2.4 f | Fault voltage emission, V <sub>rfe</sub>            | -16,5 V to +16,5 V with a source impedance of $\geq$ 1,0 k $\Omega$ |

| 5.3.5.2.4 g | Fault tolerance, R <sub>rft</sub>                   | Short circuit to ground                                             |

#### Table 6: TSM2 receiver characteristics

#### 5.3.5.3 Harness

5.3.5.3.1 Wire type

The wire type shall be twisted n-tuple.

#### 5.3.5.3.2 Core to core capacitance

The capacitance  $C_{CC}$  measured between the two core wires shall be less than or equal to 1 nF.

#### 5.3.5.4 Interface arrangement

The electrical interface arrangement is specified in Figure 14.

NOTE Circuitry is indicative only; other implementations meeting the above requirements are not excluded.

Figure 14: TSM2 interface arrangement

#### 5.3.5.5 TSM examples

#### 5.3.5.5.1 TSM1 examples

All thermistors of NTC type show a quasi-exponential temperature sensitivity in  $\Delta R_{th}/R_{th}$  of roughly 4 %/°C or one decade per 60 °C. That means that when using an NTC thermistor for a TSM1 channel, Figure 12 can be used as a general indication of accuracy in temperature by:

- rescaling the y-axis by a factor 1°C/0,04,

- exchanging the logarithmic x-axis with a linear temperature scale where minimum point of  $|\Delta R_{th}/R_{th}|$  is set to thermistor temperature at  $R_{NORM}$  and one decade corresponds to 60°C.

4K3A354 (ESCC Detail Specification No. 4006/013, variant 04) is a thermistor with nominally 4 k $\Omega$  resistance at 25°C. Figure 15 shows temperature accuracy2 specifically of a 4K3A354 thermistor connected to a TSM1 channel specified with RNORM = 4 k $\Omega$ .

YSI44907 is a thermistor with nominally 10 k $\Omega$  resistance at 25°C. Figure 16 shows temperature accuracy specifically of a YSI44907 thermistor connected to a TSM1 channel specified with RNORM = 10 k $\Omega$ .

As shown in the two examples, the accuracy in terms of temperature becomes quite similar for different NTC thermistor types, provided that  $R_{NORM}$  is selected per type for the same temperature range.

Figure 15: Example TSM1 and 4K3A354 thermistor

<sup>&</sup>lt;sup>2</sup> The figure does not include any inaccuracy of the sensor itself.

#### Figure 16: Example TSM1 and YSI44907 thermistor

#### 5.3.5.5.2 TSM2, PT1000

The platinum temperature sensors show fairly constant temperature sensitivity in  $R_{th}$  of roughly 0.004  $\cdot R_0 / \circ C$ , where  $R_0$  is the nominal resistance (at 0 °C).

PT1000 is a platinum sensor with nominally 1000  $\Omega$  resistance at 0 °C. Figure 17 shows temperature accuracy<sup>3</sup> specifically of a PT1000 connected to a TSM2 channel specified with  $R_{MAX} = 1700 \Omega$ .

$R_{MAX} = 1700 \Omega$  for the PT1000 sensor covers the temperature range up to +183 °C.

Figure 17: Example TSM2 and PT1000 thermistor

<sup>&</sup>lt;sup>3</sup> The figure does not include any inaccuracy of the sensor itself.

## 6 Bi-level discrete input interfaces

## 6.1 Bi-level discrete monitor (BDM) interface

#### 6.1.1 Overview

The bi-level discrete monitor (BDM) interfaces are used for reasonably static, discrete status and telemetry monitoring by the core element. The monitored signal is bi-level discrete in that it can take only two values, high or low, indicated by the signal voltage.

The bi-level discrete interface consists of a signal, BL\_DATA\_IN, which is generated by the peripheral element. This signal is sampled periodically by the core element.

In a practical implementation, a number of bi-level discrete interfaces can be aggregated to form a multiple bit data word in the core element.

The bi-level discrete input interface consists of a signal, BL\_DATA\_IN, which can assume two values, high or low, with respect to the signal reference. This signal is maintained continuously by the peripheral element and can be sampled at any time by the core element.

On sampling, the core element encodes the BL\_DATA\_IN value into a single binary bit of data which can be embedded in a larger data word.

There are no timing parameters associated with this interface. The BL\_DATA\_IN signal is maintained continuously by the peripheral element and can generally be regarded as static. However, if the BL\_DATA\_IN signal is sampled during a transition from one level to the other, the result determined by the core element can be invalid.

### 6.1.2 Bi-level discrete monitor interface

#### 6.1.2.1 Bi-level discrete monitor input interface - BL\_DATA\_IN signal

The peripheral element shall

- a. provide a BL\_DATA\_IN signal, and

- b. continually maintain such signal in one of two states, high (logical '1') or low (logical '0').

#### 6.1.2.2 BDM electrical characteristics

#### 6.1.2.2.1 Source circuit

The source circuit shall meet the characteristics specified in Table 7.

| Reference   | Characteristic                            | Value                                                                     |

|-------------|-------------------------------------------|---------------------------------------------------------------------------|

| 6.1.2.2.1 a | Circuit type                              | Single ended                                                              |

| 6.1.2.2.1 b | Transfer                                  | DC coupled                                                                |

| 6.1.2.2.1 c | Zero reference                            | Signal ground                                                             |

| 6.1.2.2.1 d | Low output voltage, V <sub>Lout</sub>     | 0 V to +0,5 V                                                             |

| 6.1.2.2.1 e | High output voltage, V <sub>Hout</sub>    | 2,4 V to +5,5 V,<br>into a load of 100 kΩ or greater                      |

| 6.1.2.2.1 f | Output impedance, Z <sub>out</sub>        | $\leq 5 \ k\Omega$                                                        |

| 6.1.2.2.1 g | Fault voltage emission, V <sub>sfe</sub>  | -1 V to +7 V                                                              |

| 6.1.2.2.1 h | Fault voltage tolerance, V <sub>sft</sub> | -17,5 V to +17,5 V with an overvoltage source impedance of 1,0 k $\Omega$ |

#### **Table 7: BDM source characteristics**

#### 6.1.2.2.2 Receiver circuit

The receiver circuit shall meet the characteristics specified in Table 8.

| Reference   | Characteristic                                       | Value                                                                                                                                              |

|-------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.1.2.2.2 a | Circuit type                                         | Differential receiver with multiplexed inputs                                                                                                      |

| 6.1.2.2.2 b | Transfer                                             | DC coupled                                                                                                                                         |

| 6.1.2.2.2 c | Low level differential input voltage, $V_{Lin}$      | 0 V to 0,9 V                                                                                                                                       |

| 6.1.2.2.2 d | $\begin{array}{llllllllllllllllllllllllllllllllllll$ | 2,0 V to 5,5 V                                                                                                                                     |

| 6.1.2.2.2 e |                                                      | -1 V to 1 V up to 1 kHz rolling-off at 20 dB/decade up to 1 MHz                                                                                    |

| 6.1.2.2.2 f | Input impedance, Z <sub>in</sub>                     | During acquisition: $\geq 100 \text{ k}\Omega$<br>Outside acquisition: $\geq 100 \text{ k}\Omega$<br>DHS with power off: $\geq 10 \text{ k}\Omega$ |

| 6.1.2.2.2 g | Fault voltage emission, $V_{rfe}$                    | -16,5 V to +16,5 V with a series impedance of $\geq$ 1,0 $k\Omega$                                                                                 |

| 6.1.2.2.2 h | Fault voltage tolerance, V <sub>rft</sub>            | -2 V to +8 V                                                                                                                                       |

#### **Table 8: BDM receiver characteristics**

#### 6.1.2.3 Harness

#### 6.1.2.3.1 Wire type

- a. Both twisted pair and twisted shielded pair lines may be used.

- b. Shields shall be connected to structure ground on source and receiver side.

#### 6.1.2.3.2 Core to shield capacitance

If shielded pair is used, the capacitance  $C_{CS}$  measured between the core wire and the shield shall be  $\leq 2 \ nF.$

#### 6.1.2.3.3 Core to core capacitance

If unshielded pair is used, the capacitance  $C_{CC}$  measured between the two core wires shall be  $\leq 1 \mbox{ nF}.$

#### 6.1.2.4 Interface arrangement

The electrical interface arrangement is depicted in Figure 18. The figure shows a specific implementation as example, but other implementations conforming to the requirements are not excluded.

### 6.2 Bi-level switch monitor (BSM) interface

#### 6.2.1 General principles

The bi-level switch monitor (BSM) interface is used by the core element to determine the status of a switch in the peripheral element. The peripheral element of this interface is entirely passive, consisting only of a single pole switch electrically isolated from all other components of the peripheral element.

This interface is used by the core element to determine the status of switches and relays in the peripheral element and has the advantage that it can be operated even when the peripheral element is powered down.

The switch status interface is entirely driven and operated by the core element. The core element provides a continuous reference voltage signal, and periodically samples the input signal and compares it to the reference. The result is encoded into a binary bit to indicate whether the switch was closed or open.

There are no timing constraints related to this interface since the switch status being monitored is normally static or changing infrequently. However, if the input signal is sampled while the switch status is changing, the result can be invalid.

The signal interface receiver is similar to a bi-level discrete (BDM) input with the following exceptions:

- Ground is referred to receiver (instead of source) ground.

- It is biased to a high level, when it is not being driven, by the connection of the input to a reference voltage through a resistance. When the switch contact is closed, the input signal is forced to a low level by presented low impedance.

The interface receiver converts such input signal in one of two digital states, high (logical '1') for switch source open status, or low (logical '0') for switch source closed status.

In case of specific needs, opto-couplers can be used. In that case the specific interfaces are defined on a system basis, thus they are not covered by this Standard.

#### 6.2.2 Bi-level switch monitor interface

#### 6.2.2.1 Source circuit

The source circuit shall meet the characteristics specified in Table 9.

Table 9: Switch source characteristics

| Reference | Characteristic                             | Value                                                                     |

|-----------|--------------------------------------------|---------------------------------------------------------------------------|

| 6.2.2.1 a | Circuit type                               | Floating Relay contact                                                    |

| 6.2.2.1 b | Transfer                                   | DC coupled                                                                |

| 6.2.2.1 c | Operating current, I <sub>op</sub>         | Up to 10 mA                                                               |

| 6.2.2.1 d | Operating voltage (open circuit), $V_{op}$ | Up to 15 V                                                                |

| 6.2.2.1 e | Switch closed resistance, R <sub>C</sub>   | $\leq 50 \ \Omega$                                                        |

| 6.2.2.1 f | Switch open resistance, Ro                 | $\geq 1 M\Omega$                                                          |

| 6.2.2.1 g | Fault voltage tolerance, $V_{sft}$         | -17,5 V to +17,5 V with an overvoltage source impedance of 1,0 k $\Omega$ |

#### 6.2.2.2 Receiver circuit

The receiver circuit shall meet the characteristics specified in Table 10.

Table 10: Switch receiver characteristics

| Reference | Characteristic                           | Value                                                               |

|-----------|------------------------------------------|---------------------------------------------------------------------|

| 6.2.2.2 a | Circuit Type                             | Single ended receiver with pull-up resistor                         |

| 6.2.2.2 b | Transfer                                 | DC coupled                                                          |

| 6.2.2.2 c | Zero reference                           | Signal ground                                                       |

| 6.2.2.2 d | Output current, I <sub>out</sub>         | 0,1 mA to 10 mA (when contacts closed)                              |

| 6.2.2.2 e | Output voltage, V <sub>out</sub>         | < 15 V (when contacts open)                                         |

| 6.2.2.2 f | Fault voltage emission, V <sub>rfe</sub> | -16,5 V to +16,5 V with a source impedance of $\geq$ 1,0 k $\Omega$ |

| 6.2.2.2 g | Fault tolerance, V <sub>rft</sub>        | Short circuit to ground                                             |

#### 6.2.2.3 Harness

#### 6.2.2.3.1 Wire type

The wire type shall be twisted n-tuple type.

6.2.2.3.2 Core to core capacitance

The capacitance  $C_{CC}$  measured between the two core wires shall be  $\leq 1$  nF.

#### 6.2.2.4 Interface arrangement

The electrical interface arrangement is depicted in Figure 19, which shows specific implementation to be taken as example, but other implementations conforming to requirements are not excluded.

Figure 19: Switch status circuit interface arrangement

## 7 Pulsed command interfaces

## 7.1 High power command (HPC) interfaces

## 7.1.1 General principles

The high power pulse (HPC) command interfaces are intended for load driving interfaces and, for example, can be used to switch relays or similar loads. The high current capabilities of these interfaces lead to their protection against short circuiting and against failure in a high current mode.

The high power pulse command consists of a single signal, HPC\_OUT(H), generated by the core element. This is connected by a single ended circuit to the input at the peripheral element. The interface is entirely controlled from the core element.

Three classes of HPC are defined here:

- LV-HPC : low voltage HPC (subclause 7.1.3),

- HV-HPC : high voltage HPC (subclause 7.1.4), and

- HC-HPC : high current HPC (subclause 7.1.5).

## 7.1.2 High power command interface

#### 7.1.2.1 High power pulse command - HPC\_OUT(H) signal

The core element shall

- a. provide an HPC\_OUT(H) signal, and

- b. drive such a signal.

#### **7.1.2.2** High power pulse command - HPC\_OUT(H) signal passive state The passive state of the HPC\_OUT(H) signal shall be low.

#### 7.1.2.3 High power pulse command - HPC\_OUT(H) signal active state

The active state of the HPC\_OUT(H) signal shall be high.

#### 7.1.2.4 High power pulse command output – driver unpowered

The HPC\_OUT(H) output signal shall be in passive state when the driver is unpowered.

#### 7.1.2.5 High power pulse command output - failure mode

The design of the high power pulse command interface shall ensure that no failure mode results in the output being permanently active (high state).

#### 7.1.2.6 High power command configuration

- a. The high power discrete pulse command source shall be referenced to source signal ground.

- b. The load shall be isolated from any user electrical reference.

#### 7.1.2.7 High power command transient protection

Both the high power pulse command source and receiver shall be equipped with circuits to suppress any switching transients.

NOTE This is particularly important to suppress transients due to inductive loads such as relays, which can cause the current

drive capability, or the overvoltage capability of the source to be exceeded.

#### 7.1.2.8 High power command short circuit protection

The high power pulse command source shall be short circuit proof for short circuits to source or receiver signal ground and structure.

# 7.1.3 Low voltage high power command (LV-HPC) electrical characteristics

#### 7.1.3.1 Source circuit

The source circuit shall meet the characteristics specified in Table 11.

| Reference | Characteristics                                     | Value                                                                                     |  |  |

|-----------|-----------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|

| 7.1.3.1 a | Circuit type                                        | Single ended driver return over wire                                                      |  |  |

| 7.1.3.1 b | Transfer                                            | DC coupled                                                                                |  |  |

| 7.1.3.1 c | Active state output voltage, $V_{Aout}$             | 12 V to 16 V                                                                              |  |  |

| 7.1.3.1 d | Passive state output leakage current, $I_{Pout}$    | < 100 µA                                                                                  |  |  |

| 7.1.3.1 f | Pulse width, t <sub>P</sub>                         | 4 ms to 1024 ms<br>(system design<br>selectable depending on<br>receiver characteristics) |  |  |

| 7.1.3.1 g | Output voltage rise and fall times, $t_r$ , $t_f$   | 50 $\mu$ s to 2 ms when<br>connected to a resistive<br>load of 100 $\Omega$               |  |  |

| 7.1.3.1 h | Active current drive capability, I <sub>Aout</sub>  | 180 mA                                                                                    |  |  |

| 7.1.3.1 i | Free-wheeling current capability (in Passive state) | I <sub>Aout</sub> during t <sub>P</sub>                                                   |  |  |

| 7.1.3.1 j | Short circuit output current, I <sub>SC</sub>       | ≤ 400 mA                                                                                  |  |  |

| 7.1.3.1 k | Fault voltage tolerance, V <sub>sft</sub>           | 0 V to +20 V                                                                              |  |  |

| 7.1.3.11  | Fault voltage emission, V <sub>sfe</sub>            | 0 V to +19 V                                                                              |  |  |

Table 11: LV-HPC source characteristics

#### 7.1.3.2 Receiver circuit

The receiver circuit shall meet the characteristics specified in Table 12.

| Reference | Characteristics                                                          | Value                                                              |  |

|-----------|--------------------------------------------------------------------------|--------------------------------------------------------------------|--|

| 7.1.3.2 a | Circuit type                                                             | Relay or opto-coupler                                              |  |

| 7.1.3.2 b | Transfer                                                                 | DC coupled                                                         |  |

| 7.1.3.2 c | Active level at unit input terminal, $V_{Ain}$                           | 11 V to 16 V                                                       |  |

| 7.1.3.2 d | Passive current at unit input terminal (no activation), I <sub>Pin</sub> | 200 μΑ                                                             |  |

| 7.1.3.2 e | Passive level transient immunity,<br>t <sub>Ptran</sub>                  | No activation for pulses up to the active level $100 \ \mu s$ wide |  |

| 7.1.3.2 f | Load current, I <sub>load</sub>                                          | ≤ 180 mA (at 16 V)                                                 |  |

| 7.1.3.2 g | Inputs to chassis isolation, $Z_{iso}$                                   | >1 MΩ                                                              |  |

| 7.1.3.2 h | Fault voltage emission, V <sub>rfe</sub>                                 | 0 V to +19 V                                                       |  |

| 7.1.3.2 i | Fault voltage tolerance, V <sub>rft</sub>                                | 0 V to +20 V                                                       |  |

#### Table 12: LV-HPC receiver characteristics

# 7.1.4 High voltage high power command (HV-HPC) electrical characteristics

#### 7.1.4.1 HV-HPC source circuit

The HV-HPC source circuit shall meet the characteristics specified in Table 13.

| Table 13: HV-HPC source characteristics | Table 13: | <b>HV-HPC</b> source | characteristics |

|-----------------------------------------|-----------|----------------------|-----------------|

|-----------------------------------------|-----------|----------------------|-----------------|

| Reference | Characteristic                                       | Value                                                                                  |  |

|-----------|------------------------------------------------------|----------------------------------------------------------------------------------------|--|

| 7.1.4.1 a | Circuit type                                         | Single ended driver return over wire                                                   |  |

| 7.1.4.1 b | Transfer                                             | DC coupled                                                                             |  |

| 7.1.4.1 c | Active state output voltage, $V_{Aout}$              | 22 V to 29 V                                                                           |  |

| 7.1.4.1 d | $\begin{array}{llllllllllllllllllllllllllllllllllll$ | < 100 µA                                                                               |  |

| 7.1.4.1 e | Pulse width, t <sub>P</sub>                          | 4 ms to 1024 ms (system design<br>selectable depending on receiver<br>characteristics) |  |

| 7.1.4.1 f | Output voltage rise and fall times, $t_r, t_f$       | 50 $\mu$ s to 2 ms when connected to a resistive load of 200 $\Omega$                  |  |

| 7.1.4.1 g | Active current drive capability, $I_{Aout}$          | 180 mA                                                                                 |  |

| 7.1.4.1 h | Free-wheeling current capability (in passive state)  | $I_{Aout}$ during $t_P$                                                                |  |

| 7.1.4.1 i | Short circuit output current, $I_{SC}$               | ≤ 400 mA                                                                               |  |

| 7.1.4.1 ј | Fault voltage tolerance, V <sub>sft</sub>            | 0 V to +33 V                                                                           |  |

| 7.1.4.1 k | Fault voltage emission, $V_{sfe}$                    | 0 V to +32 V                                                                           |  |

### 7.1.4.2 HV-HPC receiver circuit

The HV-HPC receiver circuit shall meet the characteristics specified in Table 14.

| Reference | eference Characteristic Value                                            |                                                             |  |

|-----------|--------------------------------------------------------------------------|-------------------------------------------------------------|--|

| 7.1.4.2 a | Circuit type                                                             | Relay or opto-coupler                                       |  |

| 7.1.4.2 b | Transfer                                                                 | DC coupled                                                  |  |

| 7.1.4.2 c | Active level at unit input terminal, $V_{Ain}$                           | 21 V to 29 V                                                |  |

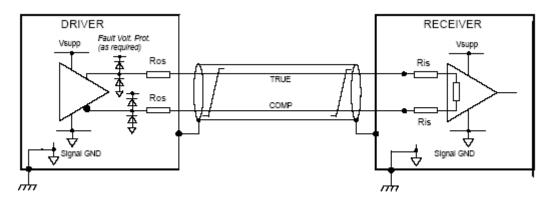

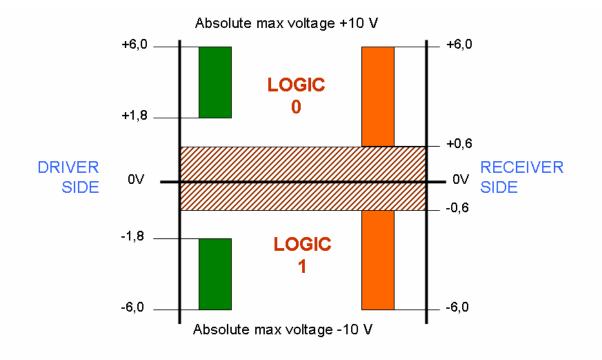

| 7.1.4.2 d | Passive current at unit input terminal (no activation), I <sub>Pin</sub> | 200 μΑ                                                      |  |